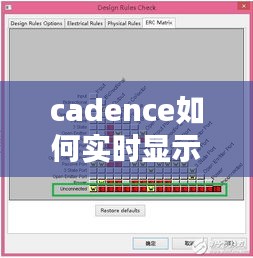

什么是Cadence DRC

Cadence Design Systems是一家全球领先的电子设计自动化(EDA)软件供应商,其产品广泛应用于集成电路(IC)设计和半导体制造领域。在Cadence的EDA工具中,DRC(Design Rule Check)是一个重要的功能,用于确保设计符合制造工艺的要求。DRC的主要目的是检查设计中的几何结构是否满足制造规则,如最小线宽、间距、电镀层厚度等,以确保设计在制造过程中能够顺利生产。

实时DRC的概念

传统的DRC流程通常是在设计完成之后,通过批处理的方式运行DRC工具来检查设计。这种方法虽然能够确保设计符合规则,但无法在设计的早期阶段提供反馈,可能导致设计在后期阶段需要大量的修改。为了提高设计效率和缩短设计周期,实时DRC应运而生。实时DRC允许设计者在设计过程中实时检查设计规则,及时发现并修正错误,从而提高设计质量并缩短设计周期。

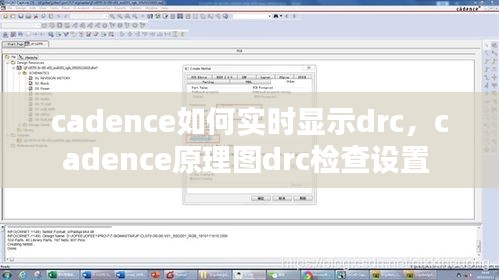

Cadence实时DRC的实现

Cadence的实时DRC功能通过以下步骤实现:

集成DRC引擎:Cadence的DRC引擎被集成到设计环境中,使得设计者可以在设计过程中直接访问DRC功能。

实时规则检查:设计者在设计过程中,每当进行设计修改时,DRC引擎会立即运行,检查新的设计是否符合规则。

即时反馈:DRC引擎在检查过程中会立即提供反馈,包括错误信息、警告信息和建议的修正方案。

可视化展示:DRC的错误和警告信息会以图形化的方式展示在设计界面上,使得设计者可以直观地看到问题所在。

实时DRC的优势

实时DRC相较于传统DRC具有以下优势:

提高设计效率:设计者可以在设计过程中及时发现并修正错误,避免后期大量修改,从而缩短设计周期。

降低设计风险:通过实时检查,可以确保设计在早期阶段就符合制造规则,降低设计风险。

提升设计质量:实时DRC可以帮助设计者更好地理解设计规则,从而提高设计质量。

优化设计流程:实时DRC可以与设计流程紧密结合,使得设计更加自动化和高效。

实时DRC的应用场景

实时DRC适用于以下场景:

复杂设计的早期阶段:在设计初期,实时DRC可以帮助设计者快速验证设计是否符合规则,避免后期修改。

迭代设计过程:在设计过程中,实时DRC可以辅助设计者进行多次迭代,确保每次迭代都符合规则。

多团队协作:实时DRC可以方便不同团队之间的协作,确保每个团队成员都能在设计过程中及时了解设计规则。

紧急设计任务:在紧急情况下,实时DRC可以快速定位问题,帮助设计者迅速解决问题。

结论

Cadence的实时DRC功能为设计者提供了一个强大的工具,使得设计过程更加高效、准确和可靠。通过实时检查设计规则,设计者可以在设计早期阶段及时发现并修正错误,从而提高设计质量并缩短设计周期。随着电子设计的日益复杂,实时DRC将成为设计过程中不可或缺的一部分。

转载请注明来自昌宝联护栏,本文标题:《cadence如何实时显示drc,cadence原理图drc检查设置 》

冀ICP备19033229号-1

冀ICP备19033229号-1